Today we have another contributor to the website.

Welcome to my good friend Equites.

The Outfoxies repair log

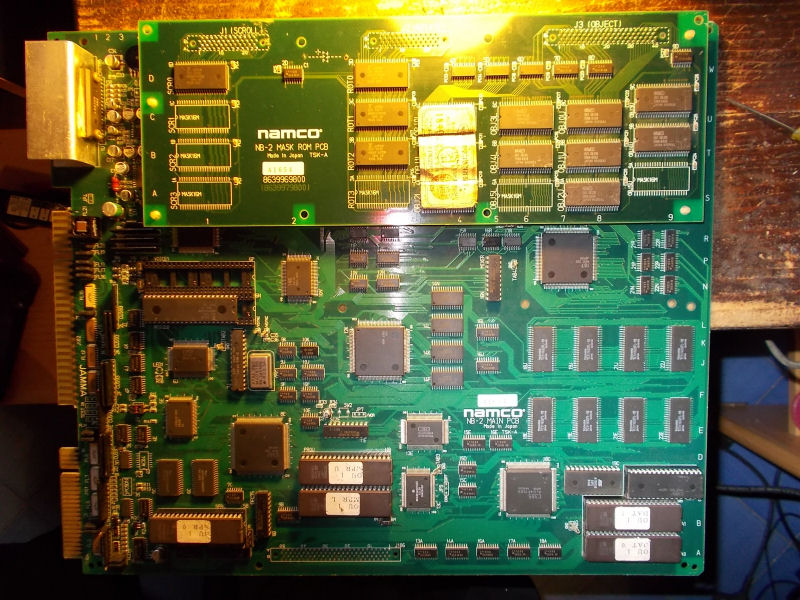

I got this mint The Outfoxies PCB for a repair from my friend Zoran :

For the uninitiated it’s a fighting game released by Namco in 1994 on Namco NB-2 hardware.The board ran well but had some inputs issue regarding the player one.Down input was not responding while left one was intermittent.This was confirmed also by switch test :

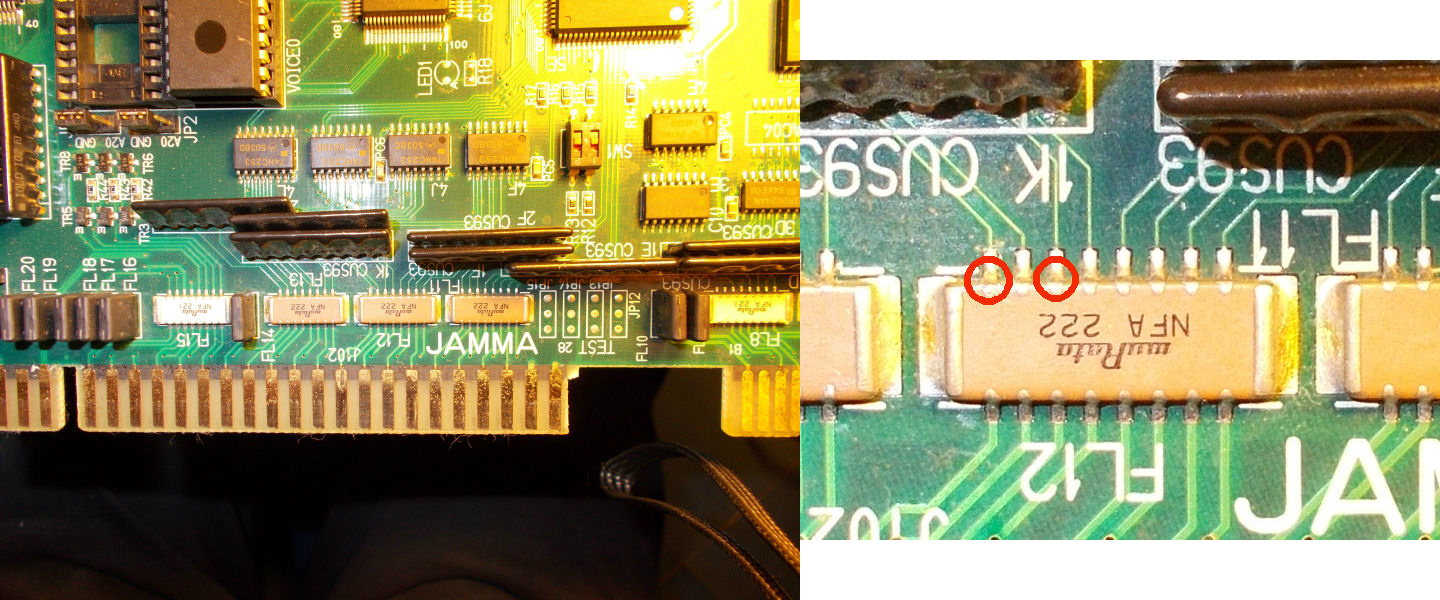

Also in this Namco hardware (like the NA-1/NA-2 and NB-1 ones) the inputs signals from JAMMA pass for first through some SMD EMI filters (which suppress high frequency interferences).Using a multimeter revealed that JAMMA pin 19 and 20 parts side had continuity with the inputs of the EMI filter @FL12 but the outputs lost their connection with the pads:

Restablishing the lost connection with a bit of AWG30 wire fixed the issue completely:

Volfied PAL dumps verified and converted

Today I could successfully verify and convert (using the PALTOGAL utility) into GAL16V8 the Volfied PAL dumps submitted some time ago by Andreas.I added proper labelling as well.So my .JED are going to replace his original PAL16L8 dumps.

Rolling Thunder custom ‘130’ replacement board PAL dumps added

Yesterday I dumped and successfully reversed into GAL16V8 the two secured PAL16L8 present on a piggyback board that replaces the custom ‘130’ on an original Namco Rolling Thunder PCB.Picture of the replacement board has been uploaded to the database as well.

This is the first in hopefully a series of posts regarding the Rainbow Islands hardware.

I have no time frame in mind for releasing these posts and I will do them when I have any particular section covered.

First up is the reset/watchdog circuit.

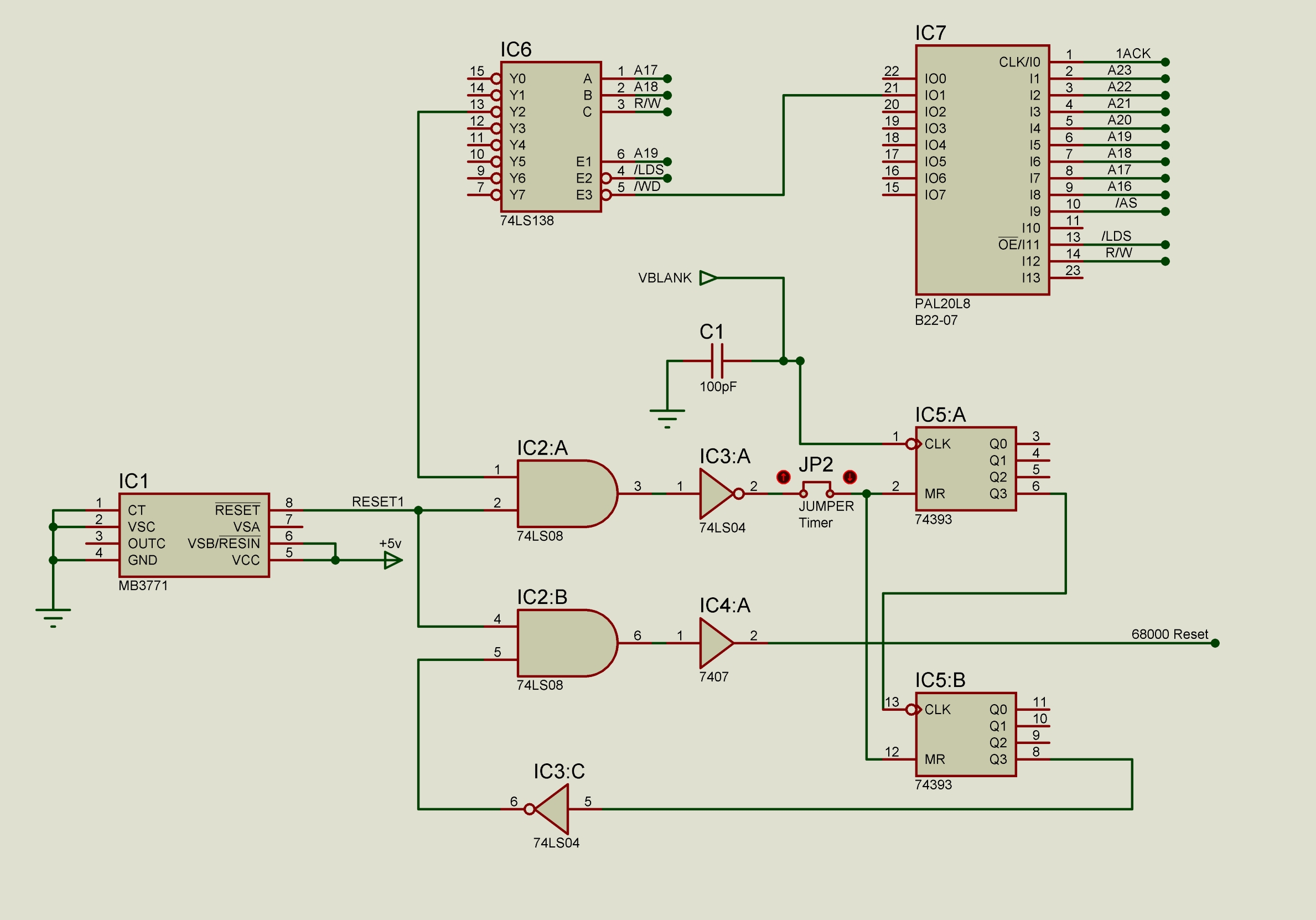

Here we have the circuit that I have drawn out.

On power up the MB3771 power supply monitor chip will keep the CPU in a reset condition by asserting a low signal to pin 4 of IC2 (74LS08 AND gate).

At the same time the master reset pin of the 74393 4-bit binary counter is held high thanks to the inverting buffer at IC3.

Note, jumper JP1 can be used to disable the watchdog although I couldn’t find a resistor tying it high which would mean if the trace was cut on JP1 the MR pin would be floating. Maybe I just cant see it.

Once the MB3771 is happy it asserts a high signal from pin 8 which will allow the 68000 CPU to run and the watchdog timer to begin.

The watchdog clock is taken from the VBLANK signal and directly clocks the first binary counter at pin 1 which in turn clocks the secondary binary counter via output pin 6.

If the master reset pin in not activated within a certain time then the counters will count up and initiate a reset.

The watchdog reset signal is achieved by writing any value to an address between $3c0000 – $3dffff.

The memory map for the watchdog is determined by the PAL20L8 device B22-07 @ IC7.

Output pin 21 is the pin concerned with this function. Here are the equations for it.

!WD = 1ACK & !A23 & !A22 & A21 & A20 & A19 & A18 & !A17 & !AS

# 1ACK & !A23 & !A22 & A21 & A20 & A19 & !A18 & A16 & !AS

# 1ACK & !A23 & !A22 & A21 & A20 & A19 & A17 & !A16 & !AS

This output goes to a 74LS138 decoder/demultiplexer. Output pin 13 is the watchdog reset output.

That’s pretty much it. Simple and nothing much out of the ordinary.